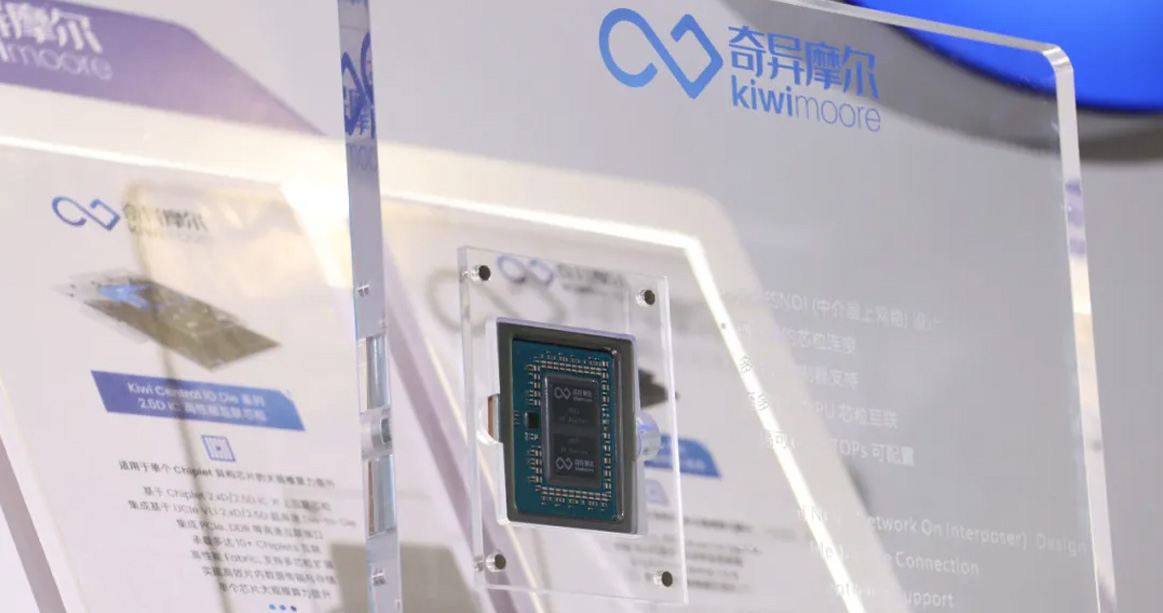

7月11日,2025年度中国创新IC-强芯奖颁奖典礼在ICDIA创芯展上揭晓获奖名单。奇异摩尔申报的Kiwi 3D Base Die产品从申报的142款产品中脱颖而出,荣获创新突破奖。据悉,“强芯评选”作为一年一度的国产IC权威推优平台,始终致力于鼓励设计创新、推动“国芯国用”、促进整机联动、加速成果转化,为国产集成电路产业的蓬勃发展注入强劲动力。

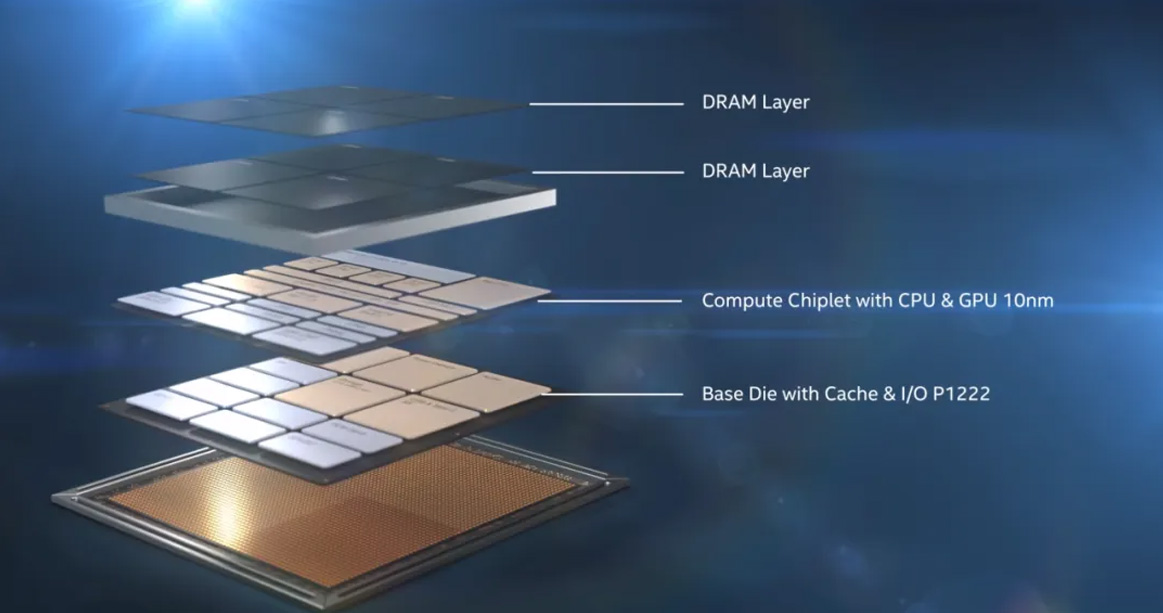

一种基于Silicon的Chiplet技术能让高性能芯片获得更高的传输速度并降低各个模块之间的传输功耗;它就是Active Silicon Interposer 又名有源基板 Base Die。举例说明,Intel 的Lakefield运用Base Die充当Compute Die的传输通道;此外与Passive Interposer有所不同的是:Base Die 集成了类似PCH的逻辑电路。由于Base Die需要很多过孔TSV,其技术难度较大。

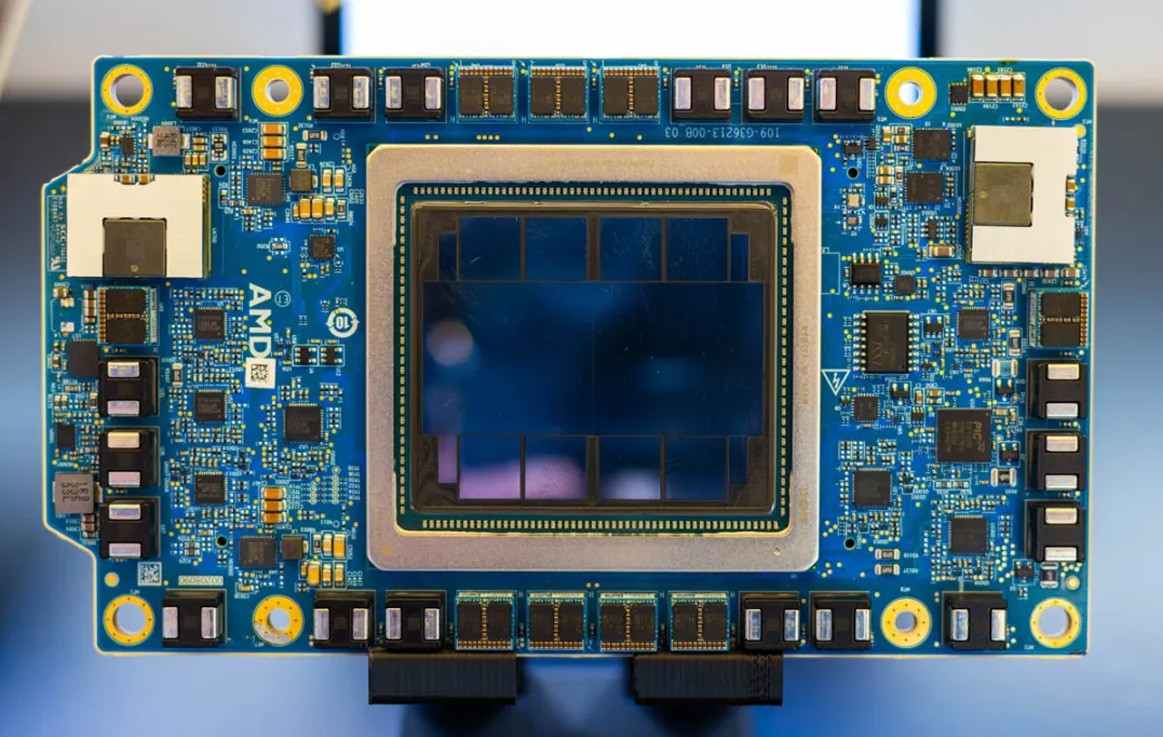

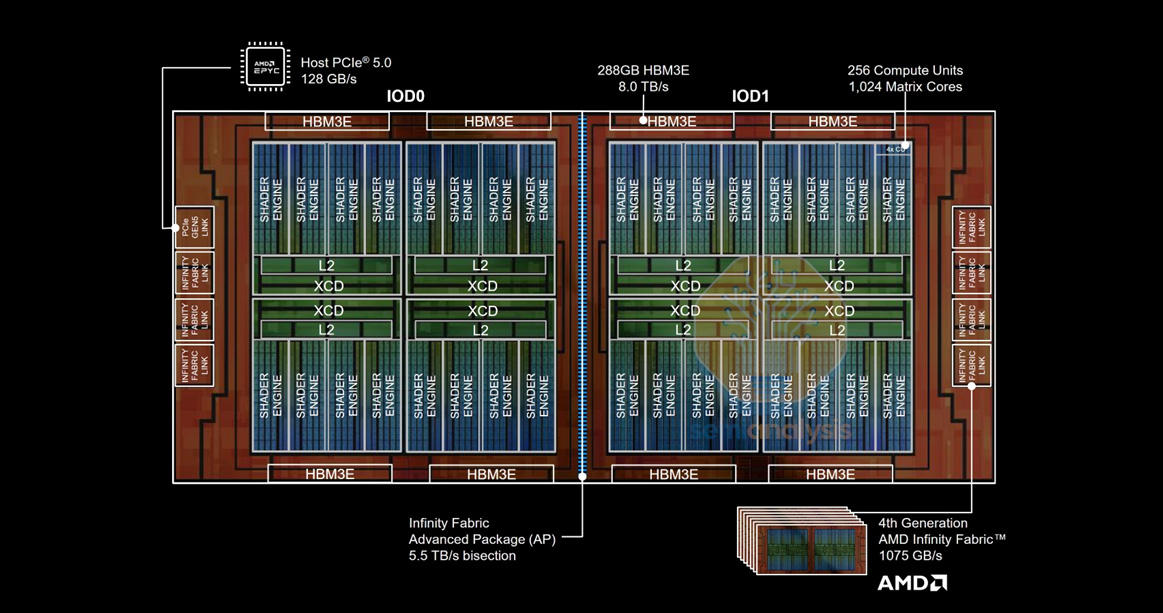

今年在Advancing AI大会上,AMD 重磅发布下一代3.5D GPU MI350 ; AMD利用MI300发布后的两年时间对芯粒架构进行了优化。从晶圆布局可见,芯片设计进行了微调:The Base Active Interposer Dies (即 3D Base Die)从四个象限合并为两个光罩尺寸的半区,HBM存储器的位置调整使得结构支撑硅片从HBM堆栈之间转移到了边角位置。

这种布局显著优化了芯粒间的通信——直接消除了整个2.5D Infinity Fabric先进封装连接的轴向传输,减少芯片边界穿越次数从而节省功耗与面积。同时解决了MI300时代对角象限芯片需要两次跨芯片跳转通信的问题。

上述the Base Active Interposer Die 和奇异摩尔Central IOD互联系列3D Base Die 互联芯粒如出一辙。Kiwi 3D Base Die是用于高性能chiplet 芯片的片内互联芯粒,支持 3D封装方式。该系列以高性能片上网络为互联核心,通过3D Die2Die 接口和封装,实现远超平面芯片的互联效率。并整合了多种等高速互联接口,搭配大容量的片上近存,可实现高效的片内数据传输调度与存储,成为高性能3D芯片的基础底座。

这种设计对3D堆叠良率提出了更高要求。AMD继续采用台积电SoIC混合键合工艺,现在每个基础芯片需要键合两倍数量的加速器复合芯片(XCD),若出现缺陷将导致更严重的良率损失和硅片浪费。AMD敢于选择这种方案,印证了台积电SoIC工艺的成熟度,以及双方长达五年(AMD作为SoIC首位客户)的深度合作。

虽然仍采用台积电N6工艺,但基础芯片已获得多项速度升级:剩余芯片间互连带宽从4.8TB/s双向等效提升至5.5TB/s;纵向扩展的Infinity Fabric速度提升20%;更重要的是内存控制器现已支持更快的HBM3E。AMD坚持使用经过验证的CoWoS-S封装技术连接3D Base Die和HBM,强调其封装尺寸与MI300保持一致。

计算芯片方面,XCD从N5工艺升级至台积电N3P节点。此次AMD仅启用了芯片上36个CU中的32个(MI300为40个启用38个)。值得注意的是,XCD在Base Die上的朝向发生变化,数据焊盘现在位于Base Die中央区域,数据经256MB末级内存附加缓存(MALL)后最终抵达HBM。

创始人田陌晨在2021年奇异摩尔创立之初就秉承为国创业的精神,深耕Chiplet赛道,奇异摩尔是国内最早布局3D Base Die 互联芯粒的科创企业之一,凭借在有源基板3D base tile的设计能力以及先进封装方面的资源整合成功联合学术界在国内首次实现三维存算一体芯片技术突破。

此次获得 “2025 中国创新 IC 强芯 - 创新突破奖”,既是对奇异摩尔的肯定,也在实际应用潜力上取得了业界的高度认可。未来公司将继续以创新为驱动,不断探索技术新场景,构建半导体产业新生态,为高性能 AI 计算领域的发展持续贡献力量,助力国产集成电路产业迈向新的高度。