破局算力瓶颈

芯粒与异构计算的先行者

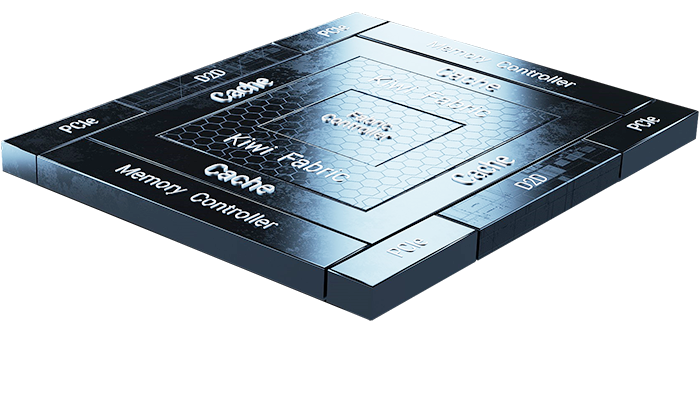

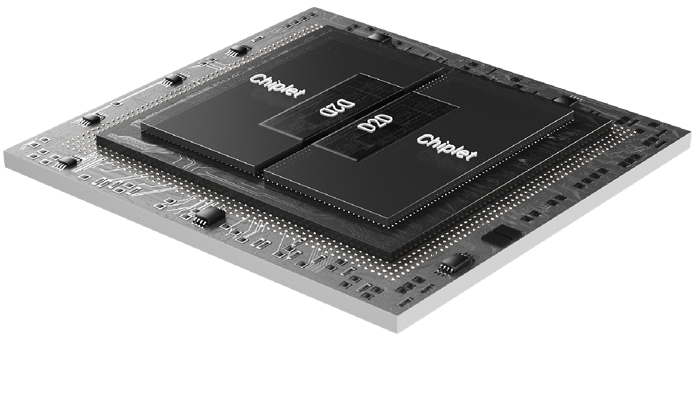

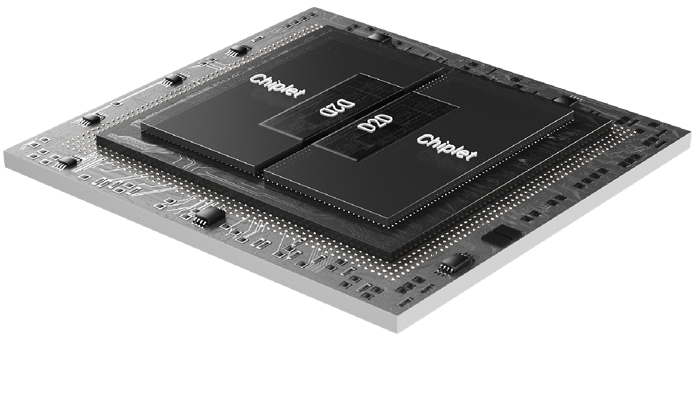

基于异构集成的片上互联芯粒

集成超高速 Die-to-Die、PCIe、DDR等高速互联接口

高性能Fabric,

支持多芯粒扩展

支持10+芯粒间互联,

实现高效片内数据传输与存储

将计算与存储紧密融合,实现TSV垂直互联

整合了PCle、DDR等高速互联接口,搭配大容量的片上近存,可实现高效的片内数据传输调度与存储

更小的芯片面积,更低的功耗,推动可持续发展

用户只需自研核心计算Die,搭载3D Base Die,实现芯粒间的高速/高密度的互联

支持16-32GT/互联带宽

和纳秒(ns)级延迟

基于UCIe标准

可灵活升级

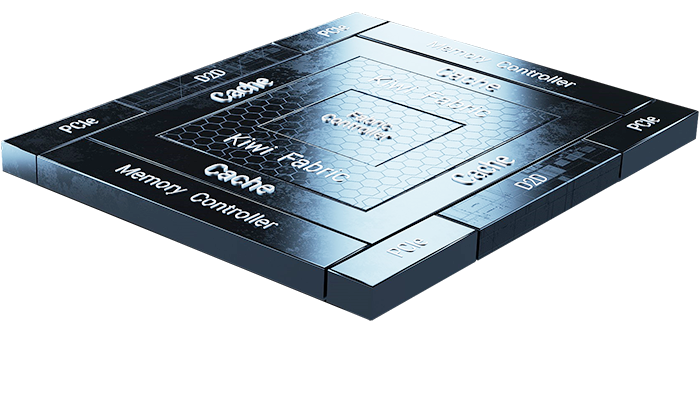

支持xPU异构芯片的C2C互联,支持高性能芯片算力扩展

支持PCIe、CXL和Streaming等主流协议