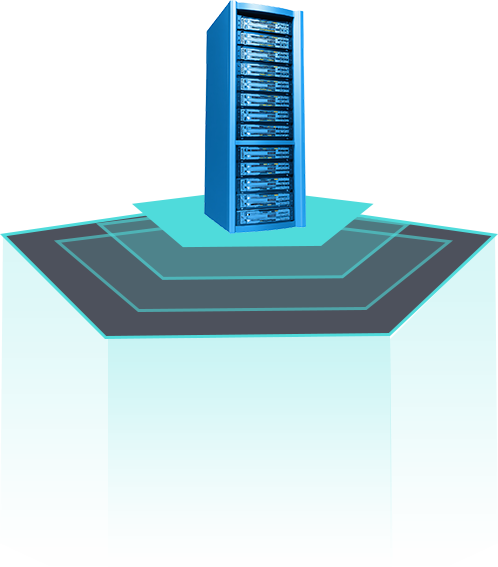

Training

Data Center

更高效可靠的

训练集群效率

Inference

Data Center

更快速经济的

推理生成能力

Edge AI

Device & Data

Center

更高效灵活的

本地化部署方案

以芯粒和Mordernized RDMA构建AI集群全栈式互联

架构及产品解决方案